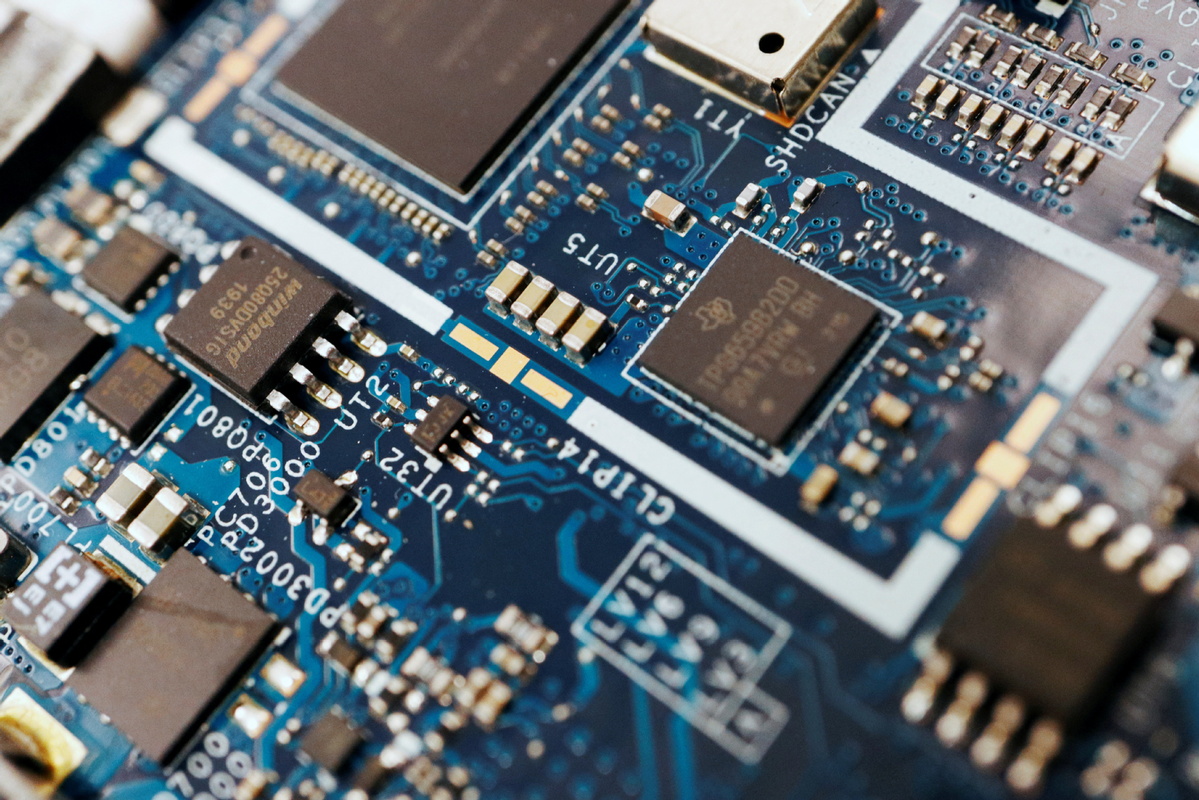

Развитие сетей-на-чип (NoC) является ключевым фактором для обеспечения производительности нейронных сетей алгоритмов. Онлайн-издание Electronics Weekly сообщает о партнерстве между компаниями Arteris и Fraunhofer IESE, которое направлено на совместную разработку окружения разработки Arteris FlexNoC и Ncore с фреймворком проектирования памяти DRAMSys от Fraunhofer IESE.

Профессор Маттиас Юнг от Fraunhofer IESE отмечает, что моделирование характеристик архитектуры ОЗУ является критическим компонентом для создания мощностно-оптимизированных архитектур SoC. Благодаря совместимости и интеграции между Arteris FlexNoC и Ncore с DRAMSys4.0, клиенты смогут оценить влияние передовых технологий ОЗУ на производительность и энергопотребление сетей-на-чип на ранних стадиях проекта.

Это партнерство поможет улучшить производительность и энергоэффективность систем и устройств, основанных на нейронных сетях и машинном обучении. Ожидается, что совместная разработка от Arteris и Fraunhofer IESE привлечет широкий интерес на рынке и станет важным шагом в развитии NoC технологий.

Читать полную новость на сайте