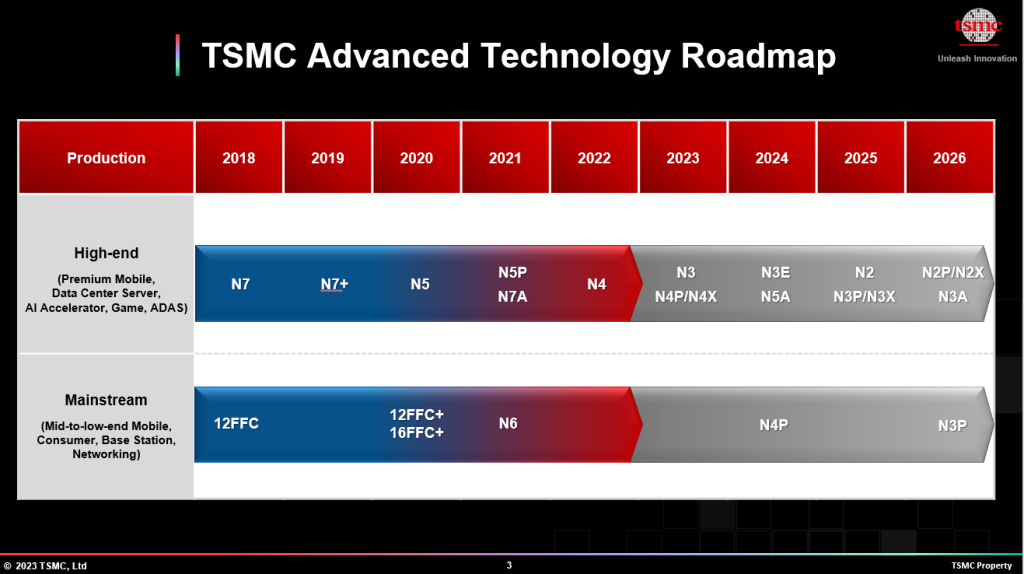

В настоящее время N3, серийное производство которого началось в четвертом квартале 2022 года, является наиболее передовым процессом.

За ним следует N3E, который прошел технологическую квалификацию и достиг своих целей по производительности и доходности. Он получил первую волну лент для клиентов и начнет массовое производство во второй половине 2023 года.

Количество новых кассет для N3E в 1,5-2 раза больше, чем для N5 за тот же период.

На подходе:

N3P, который предлагает дополнительные преимущества в производительности и площади, сохраняя при этом совместимость правил проектирования с N3E, чтобы максимизировать повторное использование IP. Его запуск в производство запланирован на вторую половину 2024 года. Он будет обеспечивать на 5% большую скорость при той же утечке, снижение мощности на 5-10% при той же скорости и в 1,04 раза большую плотность чипа по сравнению с N3E.

N3X, настроенный для приложений HPC, обеспечивает дополнительное усиление Fmax для повышения производительности перегрузки при скромных затратах. компромисс с утечкой. Это означает увеличение скорости на 5% по сравнению с N3P при напряжении питания 1,2В, с таким же улучшенным плотность стружки как N3P. N3X начнет серийное производство в 2025 году.

N3AE, первая в отрасли технология Auto Early на 3-нм техпроцессе, предлагает автомобильные PDK на основе N3E и позволяет клиентам запускать разработки на 3-нм узле для автомобильных приложений, процесс N3A, полностью сертифицированный для автомобилей, в 2025 году.

N2, основанный на нанолистовом транзисторе GAA, серийное производство которого намечено на 2025 год; N2P и N2X запланированы на 2026 год.

По словам TSMC, производительность нанолистового транзистора превысила 80% технологических целей компании, демонстрируя при этом превосходную мощность, эффективность и более низкое Vmin, что отлично подходит для энергоэффективных вычислений.

TSMC применила проект N2 в физической реализации ядра ЦП Arm A715, чтобы измерить улучшение PPA: было достигнуто увеличение скорости на 30% при той же мощности или снижение мощности на 33% при той же скорости при напряжении около 0,9 В по сравнению с предыдущим поколением. N3E, стандартная ячейка высокой плотности, 2-к-1, ребристая.

Часть технологической платформы TSMC — задняя шина питания — обеспечивает дополнительное повышение скорости и плотности по сравнению с базовой технологией.

Задняя шина питания лучше всего подходит для продуктов HPC и будет доступна во второй половине 2025 года.

Технология повышает скорость более чем на 10–12 % за счет уменьшения ИК-падения и задержек RC-сигнала, а также уменьшает площадь лицевой стороны, необходимую для логики, на 10–15 %.

Читать полную новость на сайте