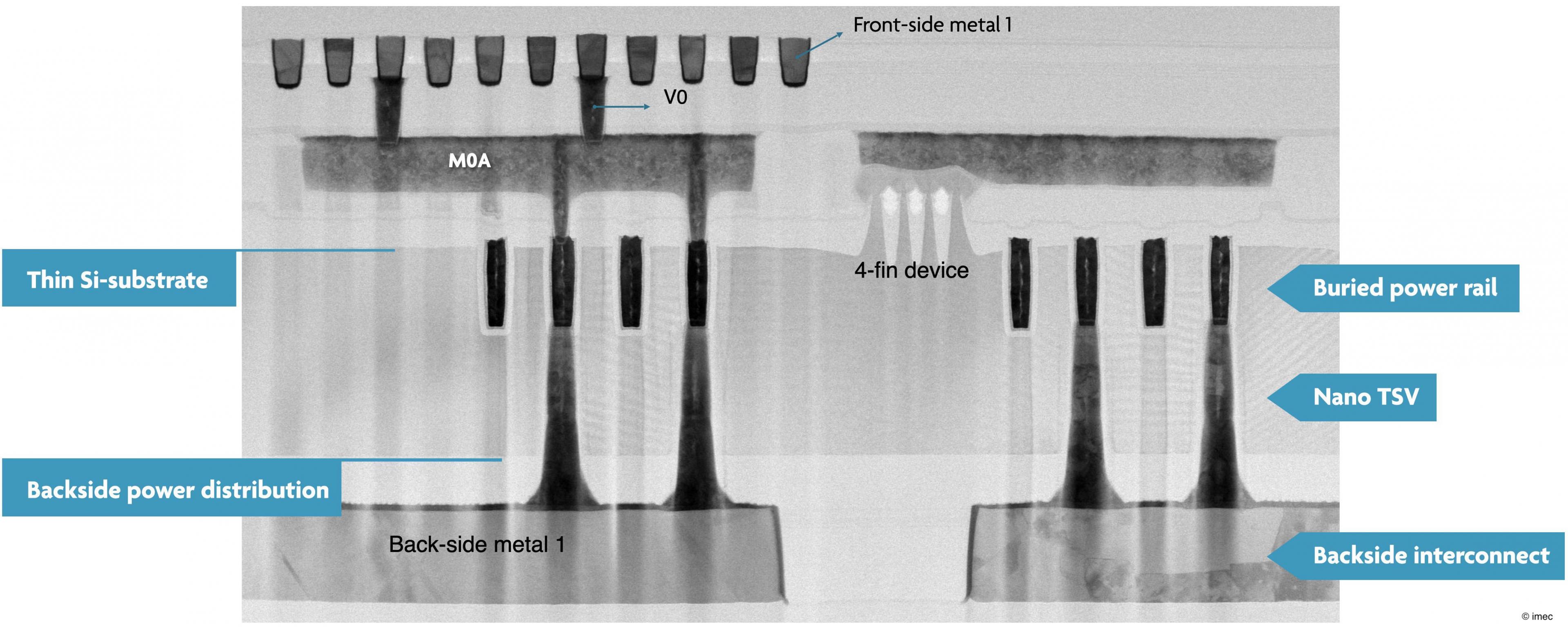

Обычные металлические слои на передней стороне пластины будут использоваться для маршрутизации сигналов, а металлические слои на задней стороне пластины будут использоваться для подачи питания.

Разделение подачи питания и маршрутизации сигналов обеспечивает более низкое падение напряжения в источнике питания (что повышает производительность) и уменьшает перегруженность металлической разводки на передней стороне.

Intel объявила, что представит это на 2-нм узле с нанолистовыми устройствами.

Изображение TEM, показывающее увеличенные полевые транзисторы FinFET, подключенные к задней и передней сторонам пластины.

Архитектура устройства, выходящая за рамки нанолистов и вилочных листов, представляет собой комплементарные полевые транзисторы (CFET), в которых устройства N и P накладываются друг на друга с использованием сложной интеграции. Возможны несколько разновидностей CFET, и мы находимся на ранних стадиях поиска путей.

Возможны несколько разновидностей CFET, и мы находимся на ранних стадиях поиска путей.

Что касается внутренней металлизации, то интеграция меди с двойным дамасским покрытием уступит место травлению металла с высоким соотношением сторон и линиям рисунка с шагом менее 20 нм.

Мы сосредоточились на использовании рутения для прямого травления металлов. Чтобы снизить сопротивление, соотношение сторон рутения будет увеличено вместе с воздушными зазорами, чтобы уменьшить влияние емкости.

Эти изменения гарантируют, что дорожная карта масштабирования внутреннего RC (сопротивление-емкость) будет продолжена для нескольких узлов.