По словам компании, это «позволило бы разработчикам микросхем производить микросхемы с более старой 180-нм и даже микронной геометрией с эквивалентной производительностью КМОП-устройств, производимых на самых современных заводах». «Например, фабрика, оснащенная 180-нм фотолитографическими шаговыми двигателями, теперь может производить устройства с размером, скоростью и производительностью 35-нм CMOS».

За его заявлениями стоят новые туннельные транзисторы компании (теперь под торговой маркой Zpolar), производственный процесс (получивший название Bizen), который делает транзисторы на старых КМОП-фабриках, и некомплементарная логическая система с низким напряжением данных с несколькими транзисторами, использующая транзисторы ( под торговой маркой ZTL).

Увеличение площади по сравнению с CMOS, по словам компании, связано с высокой проводимостью транзисторов, что приводит к уменьшению размеров транзисторов и меньшему количеству транзисторов (большинство логических элементов ZTL имеют только один), что снижает потребность в проводниках, занимающих много места в логической ячейке. Читайте дальше для более подробной технической информации.

Характеристика позволила SFN объявить о четырех пакетах дизайна ИС, фирменных ITM. Компания описывает их так:

- ITM180, который может поставлять микросхемы с производительностью 180-нм CMOS с использованием одномикронного оборудования.

- ITM35, который позволяет производить микросхемы, эквивалентные 35-нм CMOS, на 180-нм технологических узлах.

- ITM5, который обеспечивает производительность 5-нм CMOS от 28-нм шаговых двигателей

- ITMSubnm, что означает, что современные 3-нм фабрики смогут предоставлять возможности субнанометрового уровня на уровне ангстрема.

«VHDL берется в выбранный ITM — в зависимости от требований к производительности — от разработчиков микросхем», — говорится в сообщении. «ITM, который содержит полностью охарактеризованную LIB [device libraries] и ПДК [process development kit]поставляет как POR [process of reference] и информацию GDSii литейным заводам для изготовления чипа ZTL».

Можно практический пример?

SFN провела теоретическое сравнение с использованием 0,35 мкм CMOS Pentium 2 и эквивалентного устройства ZTL, оптимизированного тремя различными способами:

| CMOS 0,35 мкм Pentium 2 (Klamath) | CMOS Pentium 2 масштабируется до 1 мкм | 1 мкм ZTL скорость соответствует |

1 мкм ZTL мощность соответствует |

1 мкм ZTL линейная скорость/мощность |

|

| Среднее количество транзисторов на логический элемент | 7,5 | 7,5 | 1 | 1 | 1 |

| Количество транзисторов | 7,5 м | 7,5 м | 1м | 1м | 1м |

| Поставлять | 2,8 В | 5В | 2,7 В | 4В | 4,2 В |

| Vhi-Vlo при емкостной нагрузке. | 2,8 В | 5В | 260 мВ | 210 мВ | 180 мВ |

| Макс часы | 300 МГц | 38 МГц (8x падение через емкость) |

38 МГц | 380 МГц | 1 ГГц – 3 ГГц |

| Подниматься | 310 пс (оценка) | 2 нс (оценка) | 1,82 нс | 278 пс | 45 пс |

| падать | 310 пс (оценка) | 2 нс (оценка) | 2,24 нс | 242 пс | 47 пс |

| Распространение | 0,95 нс (оценка) | 7,5 нс (оценка) | 574 пс | 76,4 пс | 12,5 пс |

| Активная мощность на транзистор | 5,73 мкВт | 5,73 мкВт | уточняется | уточняется | уточняется |

| Общая статическая мощность | 0,1 Вт | 0,1 Вт | <0,1 Вт * | ||

| Суммарная активная мощность | 43 Вт | 43 Вт | 3,1 Вт | 42 Вт | 510 Вт |

| Средняя площадь ворот | Приблизительно 8:1 | 1 | Приблизительно 20:1 | Приблизительно 20:1 | Приблизительно 2:1 |

| Площадь штампа | 1/8 | 1 | 1/20 | 1/20 | 1/2 |

| Слои/риск | 24 (оценка) | 24 (оценка) | 8 | 8 | 8 |

| Теоретическое время выполнения заказа | 39 дней (расчетное время) | 39 дней (расчетное время) | 7,5 дней | 7,5 дней | 7,5 дней |

| Фактический / изготовленный потрясающий режим |

0,35 мкм | 1 мкм | 1 мкм | 1 мкм | 1 мкм |

| Эквивалентная экономия площади узла fab / инфраструктура сдвиг времени |

0,35 мкм +5 лет |

1 мкм 0 лет |

0,18 мкм +10 лет, включая экономию на интерконнекте |

0,18 мкм +10 лет, включая экономию на интерконнекте |

0,18 мкм +10 лет, включая экономию на интерконнекте |

| Стоимость площади штампа | 1/8 | 1 | 1/30 | 1/30 | 1/3 |

| Невероятная стоимость времени | 1 | 1 | 1/5 | 1/5 | 1/5 |

| Стоимость потрясающей геометрии | 8 | 1 | 1 | 1 | 1 |

| Общая стоимость | 1 | 1 | 1/150 | 1/150 | 1/15 |

* Если 2,5 % логики оставить включенными, а потребляемая мощность снизится в 15 раз, статическая мощность снизится с 43 Вт до 72 мВт.

(Примечание редактора: если эта таблица слишком широка для вашего браузера, скопируйте ее и вставьте в документ)

Цифры затрат в таблице основаны на упрощенной обработке пластин SFN Bizen на заводе, которая может работать на стандартных технологиях обработки кремния с использованием стандартного оборудования для обработки CMOS.

«На 180-нм заводе, использующем ITM35 и производящем чипы ZTL с производительностью, эквивалентной 35-нм CMOS, будет в десять раз меньше технологических операций, чем на фактическом 35-нм CMOS-процессе, что приведет к 10-кратному сокращению времени производства», — сказал Саммерленд. «Это означает 40-50-кратное увеличение чистой прибыли завода, преобразованного из Bizen».

По запросу он поставил цифры для этого шага уменьшения: 500 для 28nm CMOS и 50-80 шагов для Bizen.

И как долго принимать Bitzen?

«Установка потрясающей инфраструктуры ITM обычно занимает шесть месяцев», — сказал Саммерленд Electronics Weekly. «После того, как литейные заводы закончат преобразование, у них будет возможность предоставить инструменты на основе абстрактных ячеек, необходимые для преобразования существующих файлов дизайна — например, Verilog — в проекты ZTL».

Что это за логика?

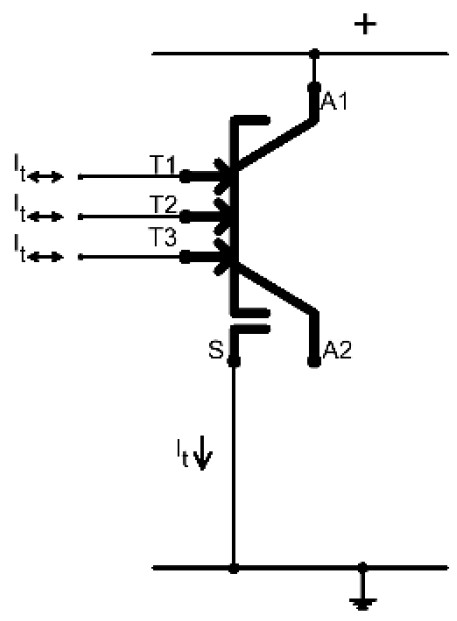

Актуальные схемы транзисторов и логики SFN еще не опубликованы, но SFN выпустила символ для трехвходового вентиля ИЛИ-ИЛИ в 2019 году (оставил).

Актуальные схемы транзисторов и логики SFN еще не опубликованы, но SFN выпустила символ для трехвходового вентиля ИЛИ-ИЛИ в 2019 году (оставил).

«Это не совсем правильно, так как задействованы переменные туннельные токи и разные характеристики переключения транзистора Zpolar», — объяснил Саммерленд (см. рисунок внизу справа).

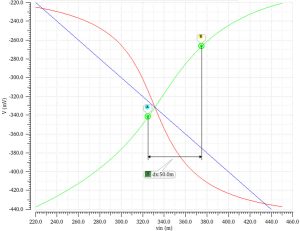

Передаточная характеристика:

Передаточная характеристика:

Входной сигнал (синий) переходит от логической 1 (325 мВ) к логическому 0 (375 мВ), в результате чего выходной сигнал колеблется от 0 до 1. Следующий выход инвертора (красный) показывает высокую крутизну

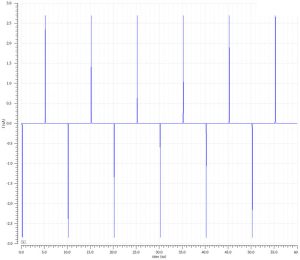

«Чтобы помочь объяснить, транзистор Zpolar имеет крутизну, с которой не могут сравниться ни биполярный PNP BJT, ни униполярный MOS. Выход затвора ZTL частично нагружен туннельным током, но в основном туннельной составляющей переменного тока. Крутая проводимость и туннелирование переменного/постоянного тока позволяют логике с одним транзистором действовать как сбалансированный привод, и при этом отсутствует сквозной ток». посмотреть ток и напряжение графики ниже.

«Показанные токи переключения ZTL не такие, как у PMOS или RTL, они похожи на CMOS» – Саммерленд.

«Показанные токи переключения ZTL не такие, как у PMOS или RTL, они похожи на CMOS» – Саммерленд.

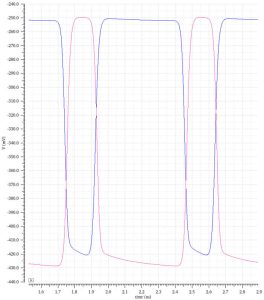

Логические элементы образованы одним транзистором, который имеет встроенное туннелирование в своей структуре. И вентиль NAND, и вентиль NOR формируются из одного транзистора с различными конфигурациями туннелирования, сказал Саммерленд Electronics Weekly. Форма волны напряжения ЗТЛ – с асимметричным ШИМ-входом

Форма волны напряжения ЗТЛ – с асимметричным ШИМ-входом

Далее он объяснил: «ZTL имеет вход с высоким импедансом с триггером волос в сочетании с выходом с низким импедансом. [see transfer function above]. Диапазон входного-выходного напряжения сосредоточен вокруг триггера волос, который производит мгновенный выходной сигнал, что обеспечивает хорошую помехоустойчивость. [see voltage waveform right]».

«Повышение скорости связано с феноменальной крутизной проводимости транзистора Zpolar», — пояснил генеральный директор компании Дэвид Саммерленд. «В сочетании с туннельной механикой, которая подает постоянный ток на крутизну, это дает огромный прирост напряжения — до 1000».

Откуда это взялось?

«Bizen разрабатывался на заводе в Великобритании в течение четырех лет, и SFN произвела тестовые пластины «золотого стандарта», которые были охарактеризованы», — сказали в SFN. «Извлеченные данные о характеристиках были помещены в книгу данных JMP и использованы для создания моделей SPICE, которые работают в среде проектирования Cadence и соответствуют результатам технологического процесса Synopsis wafer».

Компания также описала высоковольтные устройства на базе Bizen.

SFN была основана Дэвидом Саммерлендом (генеральный директор) и Сэмом Лод (главный операционный директор) в 2016 году и базируется в инновационном парке Ноттингемского университета. Компания владеет 34 патентами и в настоящее время имеет около 50 частных инвесторов — инвесторы «уже смогли продать свои акции вне рынка по текущей оценке в 100 млн долларов», утверждает компания.

SFN веб-сайт управляется его торговым подразделением Wafertrain

Уважаемый читатель! Эта технология вызвала много вопросов в Electronics Weekly Towers.

Особенно приветствуются назидательные комментарии (ниже).

/cloudfront-us-east-2.images.arcpublishing.com/reuters/VHPGVW5SAZLKZPNANSWXSZNUJY.jpg)